# W90100F PA-RISC Embedded Micro-Controller

(Preliminary)

## **Table of Contents**

| 1. GENERAL DESCRIPTION                                                                                                                                                                                                   | 5                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2. W90100 FEATURES                                                                                                                                                                                                       | 6                                             |

| 3. 208-PIN PQFP PIN CONFIGURATION                                                                                                                                                                                        | 8                                             |

| 4. W90100 PIN DESCRIPTION                                                                                                                                                                                                | 9                                             |

| 5. W90100 APPLICATION SYSTEM DIAGRAM                                                                                                                                                                                     | 11                                            |

| 5.1 W90100 System Diagram                                                                                                                                                                                                | 11                                            |

| 5.2. Reference Controller Features                                                                                                                                                                                       | 12                                            |

| 5.3 W90100 Controller Board                                                                                                                                                                                              | 12                                            |

| 6. W90100 BLOCK DIAGRAM                                                                                                                                                                                                  | 13                                            |

| 7. W90100 FUNCTIONAL DESCRIPTION                                                                                                                                                                                         | 14                                            |

| <b>7.1 DRAM Controller and ROM Controller</b><br>7.1.1 DRAM controller<br>7.1.2 ROM, FLASH, and DPI interface controller                                                                                                 | <b>14</b><br>14<br>14                         |

| 7.2 DMA Controller                                                                                                                                                                                                       | 16                                            |

| <ul><li>7.3 Timer / Counter</li><li>7.3.1 Timer Control register:</li><li>7.3.2 Timer Initial Count Register:</li></ul>                                                                                                  | <b>17</b><br>17<br>17                         |

| 7.4 Serial I/O (UART) Megacell                                                                                                                                                                                           | 18                                            |

| 7.5 Parallel Port                                                                                                                                                                                                        | 19                                            |

| 7.6 Frame Memory Reduction Module                                                                                                                                                                                        | 20                                            |

| <ul> <li>7.7 Image Enhancement Module</li> <li>7.7.1 Setup</li> <li>7.7.2 Margin Offset Control:</li> <li>7.7.3 Vertical Margin Control</li> <li>7.7.4 Input Ports</li> <li>7.7.5 Look-Up Table Memory (LUT):</li> </ul> | <b>21</b><br>21<br>21<br>21<br>21<br>21<br>22 |

| 7.7.6 OPERATING MODES                                                                                                                                                                                                    | 22                                            |

| 8. CONTROL AND STATUS REGISTER                                | 26 |

|---------------------------------------------------------------|----|

| 8.1 CPU Registers                                             | 26 |

| 8.1.1 General registers                                       | 26 |

| 8.1.2 Shadow registers                                        | 26 |

| 8.1.3 Processor Status Word (PSW)                             | 26 |

| 8.1.4 Control registers                                       | 27 |

| 8.1.5 W90100 External Interrupt Request register (EIRR; CR23) | 29 |

| 8.1.6 AIRs (Architecture Invisible Registers)                 | 29 |

| 8.2 Memory Controller Registers                               | 31 |

| 8.2.1 DRAM controller registers                               | 31 |

| 8.2.2 ROM controller registers                                | 31 |

| 8.2.3 DPI interface                                           | 32 |

| 8.3 DMA Controller (DMAC) Registers                           | 34 |

| 8.4 Timer / Counter Registers                                 | 35 |

| 8.5 Serial I/O (UART) Register Definition                     | 36 |

| 8.6 IEEE 1284 Parallel Port                                   | 39 |

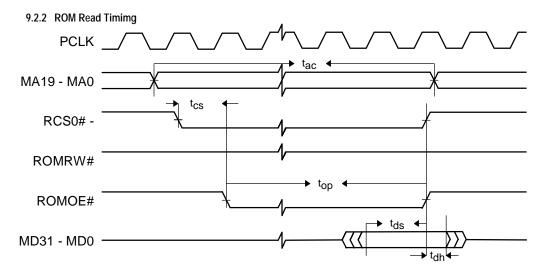

| 8.6.1 Parallel Port (Host Side) Register Definition           | 39 |

| 8.6.2 Parallel Port Interface controller (peripheral side)    | 42 |

| 8.7 Frame Memory Reduction Module Registers                   | 46 |

| 8.7.1 Control Register                                        | 46 |

| 8.7.2 Byte Count Register                                     | 46 |

| 8.7.3 Scanline Length Register                                | 46 |

| 8.7.4 JBIG Registers                                          | 48 |

| 8.8 Image Enhancement Module Registers                        | 52 |

| 8.8.1 Memory Map for RET module                               | 52 |

| 8.8.2 Control Register A (address = $0400$ )                  | 52 |

| 8.8.3 Control Register B (address = $0402$ )                  | 52 |

| 8.8.4 Control Register C (address = $0404$ )                  | 53 |

| 8.8.5 Control Register D (address = $0406$ )                  | 53 |

| 8.8.6 Control Register E (address = $0408$ )                  | 53 |

| 8.8.7 Control Register F (address = $040$ A)                  | 53 |

| 8.8.8 Control Register G (address = $040C$ )                  | 53 |

| 8.8.9 Control Register H (address = $040E$ )                  | 53 |

| 8.9 Video Interface Command/Status Registers                  | 54 |

| 8.9.1 Control Register IO1 (offset = 0300)                    | 54 |

| 8.9.2 Control Register IO2 (offset = 0301)                    | 54 |

| 8.9.3 Engine Command Register (offset = 0304)                 | 54 |

| 8.9.4 Engine Status Register (offset = $0305$ )               | 54 |

| 8.9.5 Control Register IO6 (offset = $0307$ )                 | 54 |

| 8.9.6 Control Register IO7 (offset = $0308$ )                 | 55 |

| 8.9.7 Control Register IO8 (offset = 0309)                    | 55 |

| 8.9.8 Control Register IO9 (offset = 030a)                    | 55 |

| 8.10 Parallel I/O Interface    | 56 |

|--------------------------------|----|

| 9. TIMING DIAGRAM              | 57 |

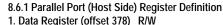

| 9.1 DRAM AC Timimg             | 57 |

| 9.2 ROM AC Timimg              | 58 |

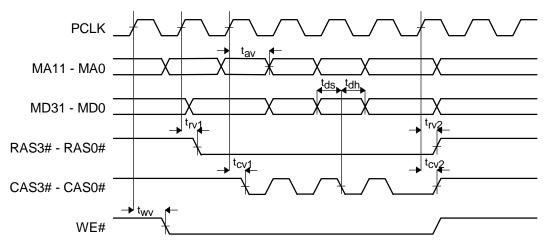

| 9.2.1 Flash ROM Write Timimg   | 58 |

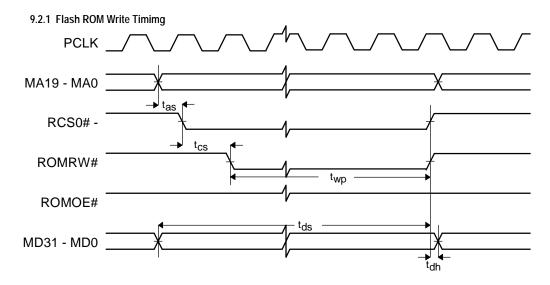

| 9.2.2 ROM Read Timing          | 58 |

| 9.3 Print Engine AC Timing     | 59 |

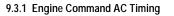

| 9.3.1 Engine Command AC Timing | 59 |

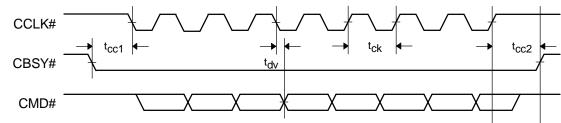

| 9.3.2 Engine Status AC Timing  | 59 |

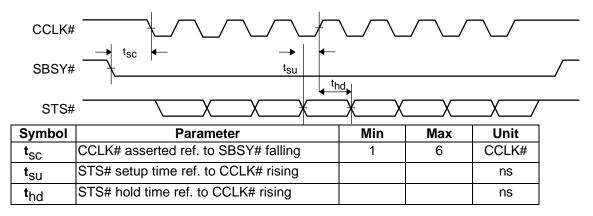

| 9.4 Video Interface AC Timing  | 59 |

| 9.5 Sram AC Timing             | 60 |

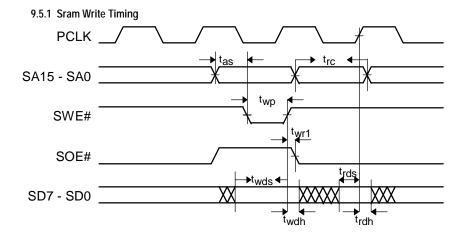

| 9.5.1 Sram Write Timing        | 60 |

## 1. General Description

The W90100 Embedded Micro-controller is part of Winbond's W90K Embedded processor family. The W90100 is a high-performance, highly integrated 32-bit processor and it is designed to be easily interfaced to a variety of laser printer mechanisms including: laser, ink-jet and thermal types.

The W90100 CPU core is based on the HP PA-RISC architecture and is upward code compatible with the W90K. The PA-RISC architecture incorporates traditional RISC elements, such as instruction pipelining, a register-to-register instruction set and a large, general-purpose register file. Separate on-chip instruction and data caches allow the W90100 to fetch an instruction and access data in a single processor cycle.

The W90100 includes several features that greatly increase performance, reduce system component count and ease the overall system design task in a printer application. These features include a DRAM controller, FLASH ROM controller, serial port with FIFO, IEEE 1284 parallel port, timer/counters, Programmable I/O port, DMA controller, DPI interface, and enhanced debug support; all features that are commonly required in general embedded applications. In addition, the W90100 supports generic printer video and communications interface signals for easy interfacing with generic laser printer engine. To further increase the overall performance of the W90100 printer system, both image enhancement, including edge enhancement and gray scale enhancement; as well as frame memory compression are integrated into the W90100 micro-controller.

## 2. W90100 Features

- PA-RISC architecture

- PA-RISC 1.1 third edition instruction set PA-RISC level zero implementation Support PA-RISC Multimedia Extension 1.0 instruction set W90K binary compatible for user software

- High-performance, singlesaclar implementation Five-stage pipeline Precise, efficient handling of pipeline stalls and exceptions Delayed branch with static branch prediction Forward: not taken; Backward: taken One-cycle stall when prediction is wrong Load Scheduling Both load and store can be queued when miss Load/store single cycle execution after previous miss

- On-chip cache memory

Internal I-cache: Direct mapped, 4 KB cache (256 entries, four words/entry) Wrap around fetching when cache miss; Cache freeze capability

- Internal D-cache: 2-way set associative, 2 KB cache X264 entries, 4words/entry) Write-back cache with write buffer; Write-through option New line send to CPU before dirty line write back

- Enhanced debug capability

Debug SFU supports both instruction breakpoint and data breakpoint Two sets of instruction breakpoint regiters are provided (Mask and Offset) Two sets of data breakpoint regiters are provided (Mask and Offset) JTAG TAP controller for JTAG ICE support IEEE 1149.1 JTAG boundary scan

- High on-chip integration and simple I/O interface

- Memory controller to interface with BAM, ROM, FLASH, and DPI interface

- Support both Fast-Page mode and EDO DRAM

- Upto 4 banks of DRAM, 64M Bytes per bank

- Support 8-bit, 16-bit, and 32-bit ROM

- Upto 4 banks of ROM or FLASH, 4M Bytes per bank

- Internal 2-channel 16-bit DMA controller

- Serial port with FIFO

- IEEE 1284 parallel port for input

- IEEE 1284 parallel port for output

- 8-bit Programmable I/O port

- Two 24-bit timer/counters

- Image Enhancement Technology

- Edge enhancement as well as 1 bit and 8 bit grayscale enhancement to enhance the output print quality.

- PowerBand® Frame Memory Reduction

- Built-in CODEC s to reduce the system memory requirements by up to 8X in printer applications.

- Direct Generic Printer Engine Interface

- Economy mode: Power down and toner saver modes for economical operation

## **Embedded Micro-Controller**

## **W90100F**

W90100 Microcontroller Feature Sets

| Basic Features                  | W90100                   |  |  |

|---------------------------------|--------------------------|--|--|

| Bus                             | CPU Bus                  |  |  |

| Data Cache                      | Yes                      |  |  |

| Size                            | 2K Bytes                 |  |  |

| Associativity                   | 2 Way                    |  |  |

| Instruction Cache               | Yes                      |  |  |

| Size                            | 4K Bytes                 |  |  |

| Associativity                   | Direct mapped            |  |  |

| Multimedia extension            | Yes                      |  |  |

| JTAG Debug support              | JTAG ICE support         |  |  |

| H/W Breakpoints                 | Yes                      |  |  |

| Instruction H/W Breakpoints     | 2 sets (mask and offset) |  |  |

| Data H/W Breakpoints            | 2 sets (mask and offset) |  |  |

| DX/2 support                    | Yes                      |  |  |

| ROMInterface                    | Yes                      |  |  |

| Banks                           | 4                        |  |  |

| Width                           | 8, 16, 32 bits           |  |  |

| Max size/bank                   | 4 MBytes/Bank            |  |  |

| Boot-up ROM Width               | 8, 16, 32 bits           |  |  |

| Burst-mode access               | Supported                |  |  |

| DRAM Interface                  | Yes                      |  |  |

| Banks                           | 4                        |  |  |

| Width                           | 32 bits                  |  |  |

| Max size/bank                   | 64 MBytes/Bank           |  |  |

| Initial /Burst access cycles    | 3/2/2/2 or 2/1/1/1       |  |  |

| DRAM Parity                     | No                       |  |  |

| On-Chip Line Store SRAM         | Yes                      |  |  |

| Width                           | 16 bits                  |  |  |

| Size                            | 8K Bytes                 |  |  |

| External CODEC SRAM Interface   | Yes                      |  |  |

| Width                           | 8-bit                    |  |  |

| Max size                        | 64K Bytes                |  |  |

| On-chip DMA                     | Yes                      |  |  |

| Total number of channels        | 2                        |  |  |

| Mem-CODEC transfer              | Yes                      |  |  |

| Mem-to-Mem transfer             | Yes                      |  |  |

| Mem-to-ECP transfer             | Yes                      |  |  |

| On-chip generic video interface | Yes                      |  |  |

| On-chip interrupt controller    | Yes                      |  |  |

| Interrupt pins                  | INT1, INT2               |  |  |

| On-chip timer                   | Yes                      |  |  |

| Number of channels              | 2 Channels (24-bit)      |  |  |

| Serial Ports                    | 1                        |  |  |

| 16550 FIFO support              | Yes                      |  |  |

| Parallel Ports                  | 2                        |  |  |

| ECP support                     | Yes                      |  |  |

| FIFOsupport                     | Yes                      |  |  |

| 1284 support                    | Yes                      |  |  |

| Endian                          | Big-Endian               |  |  |

| Operating voltage               | 5V, 3.3V                 |  |  |

| Clock speed                     | 40 MHz                   |  |  |

| Package                         | 208 PQFP                 |  |  |

| W90100 Microcontroller Feature Sets |        |  |  |

|-------------------------------------|--------|--|--|

| Advanced Features                   | W90100 |  |  |

| On-chip Codec                       | Yes    |  |  |

| JBIG                                | Yes    |  |  |

| Contone                             | Yes    |  |  |

| On-chip Enhancement Support         | Yes    |  |  |

| Edge Enhancement                    | Yes    |  |  |

| Resolution Doubling                 | Yes    |  |  |

| 300 dpi to 600 dpi                  |        |  |  |

| 600 dpi to 1200 dpi                 |        |  |  |

| Grayscale Enhancement               | Yes    |  |  |

| 1 bit                               |        |  |  |

| 8 bit                               |        |  |  |

| Toner Saver                         | Yes    |  |  |

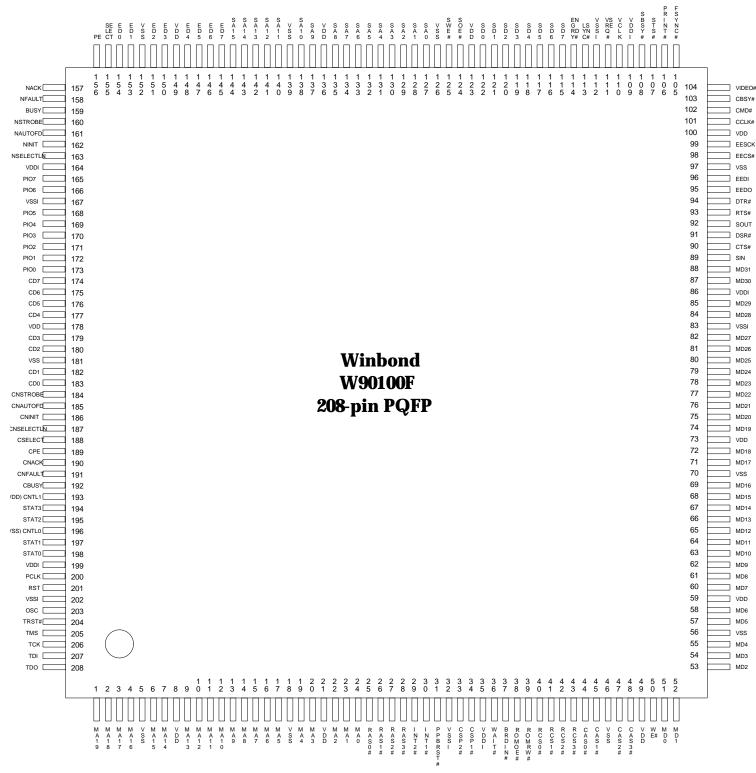

## 3. 208-Pin PQFP Pin Configuration

Figure 3.1 W90100 Pin Configuration

## 4. W90100 Pin Description

| PIN Name                   | DIR      | PIN #                           | DESCRIPTION                                        |

|----------------------------|----------|---------------------------------|----------------------------------------------------|

| JTAG Boundary Scan Inte    | rface    |                                 |                                                    |

| TCK                        | I        | 206                             | JTAG test clock input                              |

| TRST#                      | I        | 204                             | JTAG test reset input                              |

| TMS                        | I        | 205                             | JTAG test mode select input                        |

| TDI                        | 1        | 207                             | JTAG test data input                               |

| TDO                        | 0        | 208                             | JTAG test data output                              |

| CPU Signal                 |          |                                 |                                                    |

| RST                        | 1        | 201                             | RESET input                                        |

| PCLK                       | I        | 200                             | CLOCK input                                        |

| OSC                        | I        | 203                             | Oscillator input for Timer, UART, and DRAM refresh |

| STAT[0:3]                  | 0        | 198,197,195,194                 | CPU status output                                  |

| Generic Printer Engine Int | erface   |                                 | · · ·                                              |

| PRINT#                     | 0        | 106                             | Print Request                                      |

| FSYNC#                     | 1/O      | 105                             | Frame Sync                                         |

| LSYNC#                     | 1        | 113                             | Line Sync                                          |

| VIDEO#                     | 0        | 104                             | Video Data Stream                                  |

| VCLK                       | 1        | 110                             | Video Shift Rate Clock                             |

| CBSY#                      | 0        | 103                             | Command Busy                                       |

| SBSY#                      |          | 108                             | Status Busy                                        |

| CMD#/STS#                  | 1/0      | 102                             | Command/Status Data                                |

| STS#                       | 1/0      | 102                             | Status Data                                        |

| CCLK#                      | I/O      | 101                             | Command Clock                                      |

| ENGRDY_                    | 1/0      | 114                             |                                                    |

| VSREQ#                     |          |                                 | Printer Enginer Ready                              |

| ECP Interface (Peripheral  | -        | 111                             | Vsync Request                                      |

|                            |          | 450                             |                                                    |

| Busy                       | 0        | 159                             | ECP busy input signal                              |

| nFault                     | 0        | 158                             | ECP fault input                                    |

| nAck                       | 0        | 157                             | ECP acknowledge input                              |

| PError                     | 0        | 156                             | ECP parity error                                   |

| Select                     | 0        | 155                             | ECP Select                                         |

| nSelectIn                  | 1        | 163                             | ECP select output                                  |

| nInit                      | I        | 162                             | ECP initialization                                 |

| nAutoFd                    | I        | 161                             | ECP Autofeed                                       |

| nStrobe                    | I        | 160                             | ECP Strobe                                         |

| ED[0:7]                    | I/O      | 154,153,151,150,148,147,146,145 | ECP Data bus                                       |

| Centronics Output Port     |          |                                 | F                                                  |

| CBusy                      | In       | 192                             | Centronics printer busy input                      |

| CnFault                    | In       | 191                             | Centronics Error input                             |

| CnAck                      | In       | 190                             | Centronics Acknowledge input                       |

| CPE                        | In       | 189                             | Centronics Paper End input                         |

| CSelect                    | In       | 188                             | Centronics Select input                            |

| CnSelectIn                 | 0        | 187                             | Centronics Select in output                        |

| CnInit                     | 0        | 186                             | Centronics Init output                             |

| CnAutoFd                   | 0        | 185                             | Centronics auto feed output                        |

| CnStrobe                   | 0        | 184                             | Strobe pulse to write data                         |

| CD[0:7]                    | I/O      | 183,182,180,179,177,176,175,174 | Centronics Data bus                                |

| Programmable Input/Outp    | out Port |                                 | -                                                  |

| PIO[0:7]                   | I/O      | 173,172,171,170,169,168,166,165 | Programmable input/output port                     |

| Memory Controller Interfa  | ce       | 1                               |                                                    |

| RAS#[0:3]                  | 0        | 25,26,27,28                     | DRAM Row Address Strobe, Banks 0-3                 |

| CAS#[0:3]                  | 0        | 44,45,47,48                     | DRAM Column Address Strobes, Byte 0-3              |

| 0/(0//0.0)                 |          |                                 |                                                    |

| RCS#[0:3]            | 0   | 40,41,42,43                                                                                             | ROM/FLASH Chip Selects, Banks 0-3      |

|----------------------|-----|---------------------------------------------------------------------------------------------------------|----------------------------------------|

| MA[19:0]             | 0   | 1,2,3,4,6,7,9,10,11,12,13,14,15,16,17,19,<br>20,22,23,24                                                | Memory controller Memory Address bus   |

| MD[0:31]             | I/O | 51,52,53,54,55,57,58,60,61,62,63,<br>64,65,66,67,68,69,71,72,74,75,76,<br>77,78,79,80,81,82,84,85,87,88 | Memory controller Data bus             |

| ROM_OE_              | 0   | 38                                                                                                      | ROM/FLASH output enable                |

| ROM_RW_              | 0   | 39                                                                                                      | ROM/FLASH read/write control signal    |

| PPB_CSP1_            | 0   | 34                                                                                                      | DPI interface chip select 1            |

| PPB_CSP2_            | 0   | 33                                                                                                      | DPI interface chip select 2            |

| PPB_RST_             | 0   | 31                                                                                                      | DPI interface reset signal             |

| PPB_WAIT_            | 1   | 36                                                                                                      | DPI interface wait signal              |

| PPB_BRDIN_           | 1   | 37                                                                                                      | DPI interface Board exist signal       |

| PPB_INT1_            | I   | 30                                                                                                      | DPI interface interrupt 1              |

| PPB_INT2_            | I   | 29                                                                                                      | DPI interface interrupt 2              |

| CODEC SRAM interface |     |                                                                                                         |                                        |

| SA[0:15]             | 0   | 127,128,129,130,131,132,133,134,135,13<br>7,138,140,141,142,143,144                                     | CODEC SRAM address output              |

| SD[0:7]              | I/O | 122,121,120,119,118,117,116,115                                                                         | CODEC SRAM data bus                    |

| SWE                  | 0   | 125                                                                                                     | CODEC SRAM write enable                |

| SOE                  | 0   | 124                                                                                                     | CODEC SRAM output enable               |

| EEPROM interface     |     |                                                                                                         | ·                                      |

| EESCK                | 0   | 99                                                                                                      | EEPROM clock                           |

| EECS_                | 0   | 98                                                                                                      | EEPROM chip select                     |

| EEDI                 | 0   | 96                                                                                                      | EEPROM serial data output              |

| EEDO                 | I   | 95                                                                                                      | EEPROM serial data input               |

| Serial Port Signal   |     |                                                                                                         | ·                                      |

| RTS_                 | 0   | 93                                                                                                      | Serial port request-to-send output     |

| CTS_                 | I   | 90                                                                                                      | Serial port clear-to-send input        |

| DTR_                 | 0   | 94                                                                                                      | Serial port data-terminal-ready output |

| DSR_                 | 1   | 91                                                                                                      | Serial port data-set-ready input       |

| SIN                  | 1   | 89                                                                                                      | Serial port input data                 |

| SOUT                 | 0   | 92                                                                                                      | Serial port output data                |

| Power                |     |                                                                                                         |                                        |

| VDD                  | 1   | 8,21,35,49,59,73,86,100,109,123,136,149,1                                                               | 164,178,193,199                        |

| GND                  | •   | ·                                                                                                       |                                        |

| VSS                  | I   | 5,18,32,46,56,70,83,97,112,126,139,152,16                                                               | 67,181,196,202                         |

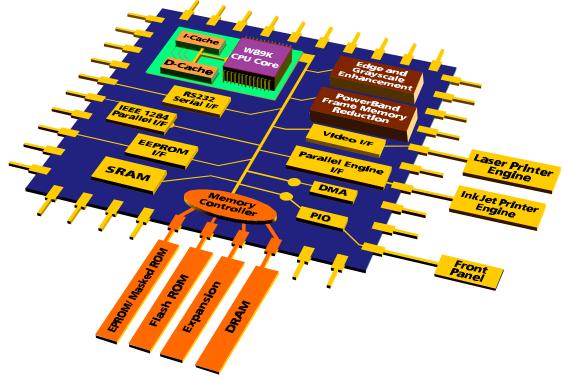

## 5. W90100 Application System Diagram

## 5.1 W90100 System Diagram

FIGURE 5.1 W90100 SYSTEM DIAGRAM

## 5.2. Reference Controller Features

#### W90100 Microcontroller Reference Board Feature Sets

| Reference Board Features                 | W90100                                       |  |  |

|------------------------------------------|----------------------------------------------|--|--|

| Input/output                             |                                              |  |  |

| Serial ports                             | 1 on chip                                    |  |  |

| Parallel ports                           | 2 on chip                                    |  |  |

| Network                                  |                                              |  |  |

| DPI daughter card                        | DPOdaughter card I/F connector on board      |  |  |

| Image enhancement                        |                                              |  |  |

| Image Enhancement Module                 | On-chip XLI image enhancement                |  |  |

| PowerBand compression Codec              |                                              |  |  |

| Contone                                  | On-chipPipeline proprietary contone codec    |  |  |

| 1-bit                                    | On-chip Pipeline proprietary JBIG-like codec |  |  |

| Video engine I/F                         | On-chip                                      |  |  |

| Connectors                               |                                              |  |  |

| Serial                                   | DB-25                                        |  |  |

| Parallel 1 (printer input)               | Centronics 36                                |  |  |

| Parallel 2 (engine i/f)                  | 36 pin header (male)                         |  |  |

| Network DPO interface header             |                                              |  |  |

| Video i/f NEC and SHARP Engine Connector |                                              |  |  |

TABLE 5.2 W90100 CONTROLLER BOARD FEATURE SET

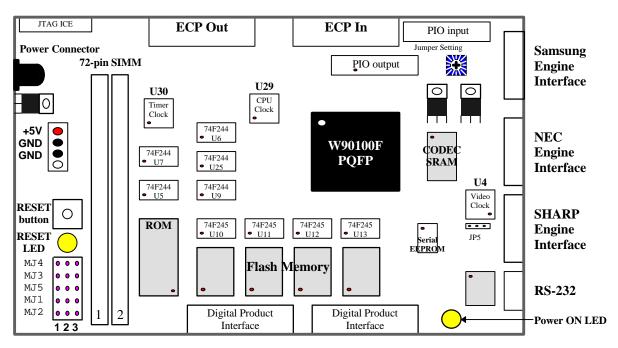

## 5.3 W90100 Controller Board

## FIGURE 5.3 W90100 CONTROLLER BOARD

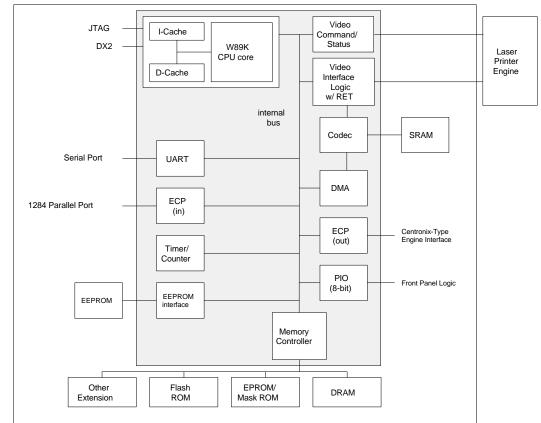

## 6. W90100 Block Diagram

FIGURE 6.1 W90100 BLOCK DIAGRAM

## 7. W90100 Functional Description

The W90100 significantly reduces overall system cost because it integrates most printer system functions onto a single chip.

## 7.1 DRAM Controller and ROM Controller

#### 7.1.1 DRAM controller

The DRAM controller supports four separate banks of dynamic memory. Either X8 or X32 SIMMs are supported. CAS#-before-RAS# refresh cycles are performed periodically, as determined by the refresh timer. The DRAM controller must arbitrate between access requests and refresh requests. Both EDO and page mode DRAM's are supported.

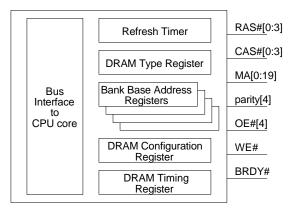

#### FIGURE 7.1 DRAM CONTROLLER BLOCK DIAGRAM

#### 7.1.2 ROM, FLASH, and DPI interface controller

The ROM controller also supports upto four banks of ROM and the ROM can be 8-bit, 16-bit, or 32-bit.

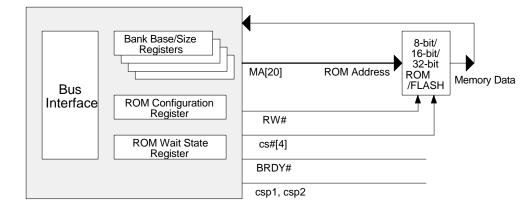

#### FIGURE 7.2 ROM CONTROLLER DIAGRAM

For each bank of ROM, two registers are used to specify the bank address range:

ROM Bank Base Address Register.

ROM Bank Size Register.

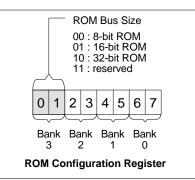

ROM Configuration Register is used to program the ROM data bus size of each bank.

#### FIGURE 7.3 ROM CONFIGURATION REGISTER PROGRAMMING

ROM Read Wait State Register is used to program the number of wait states needed to access ROM. The cycle needed for writing the ROM is fixed.

Also, there are two base address registers provided for the DPI interface. The DPI interface always use 16-bit access for memory access and 8-bit access for the registers. The base register must be programmed with a value of 128K boundary

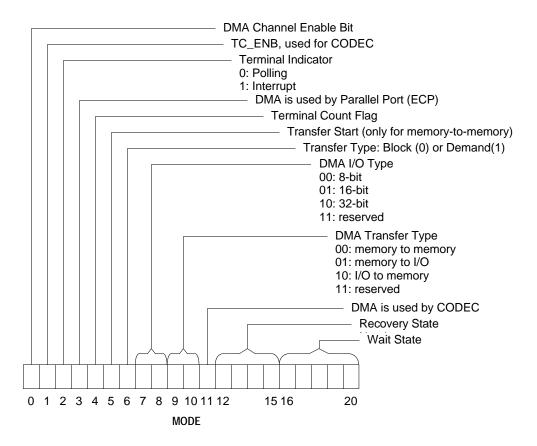

## 7.2 DMA Controller

The DMA Controller megacell provides two DMA channels to support DMA transfers between 16-bit I/O devices and main memory. The DMA mechanism will provide two different methods for performing DMA transfers: demand-mode transfers and block-mode transfers. The DMAC hardware is responsible for synchronizing transfers with memory or I/O devices.

When the DMAC is configured for demand mode, a device requests a DMA transfer with a request input (DREQ1:0#). The DMAC acknowledges the requesting device with an acknowledge signal (DACK1:0#) when the requesting device is accessed.

In block mode, DMA transfers are not requested by an external device. The DMA operation is initiated by software and continued until terminated or suspended. The DMA operation is started when the enable bit in the Configuration Register is set.

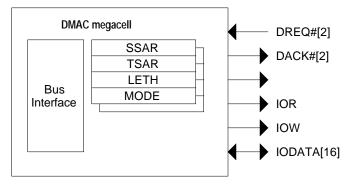

#### FIGURE 7.4 DMA CONTROLLER

In programming the megacell registers, the register address is defined by the BASE register plus the offset value.

## 7.3 Timer / Counter

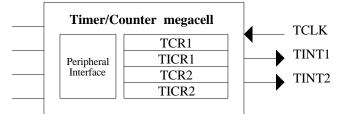

#### FIGURE 7.5 TIMER/COUNTER MEGACELL

Two 24-bit decrementing timers are implemented. When the timer's interrupt enable bit is set to one and the counter decrements to zero, the timer will assert the associated interrupt signal. The interrupt signal will assert one of the 32 external interrupts defined by the EI bits in the control register. When a timer reaches zero, the timer hardware reloads the counter with the value from the timer initial count register and continues decrementing.

Each timer is controlled and initialized by two registers: a timer control register and an timer initial count register. These registers are all memory mapped I/O registers.

7.3.1 Timer Control register:

| 0  | 1  | 2  | 3 | 4 | 23       | 24         | 31 |

|----|----|----|---|---|----------|------------|----|

| TI | CE | IE |   |   | reserved | pre-scalar |    |

|    |    |    |   |   | TCR      |            |    |

Pre-Scalar (PS): A pre-scalar value can be used to divide the input clock.

Interrupt Enable bit (IE): When IE is set to one and the counter decrements to zero, the timer asserts its interrupt signal to interrupt the CPU.

Counter Enable bit (CE): Setting the CE bit to one causes the timer to begin decrementing. Setting the CE bit to zero stops the timer.

Timer Interrupt bit (TI): The timer sets this bit to one to indicate that it has decrement to zero. This bit remain one until software sets it to zero.

7.3.2 Timer Initial Count Register:

| 0 7      | 8                   | 31 |

|----------|---------------------|----|

| reserved | Timer Initial Count |    |

|          | TICR                |    |

A 24-bit read/write register for the initial counter value.

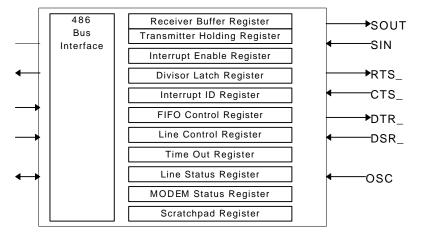

## 7.4 Serial I/O (UART) Megacell

The serial I/O (UART) megacell implements a full-duplex, bi-directional UART with FIFO.

Serial I/O (UART) megacell

FIGURE 7.6 SERIAL I/O (UART) WITH FIFO

## 7.5 Parallel Port

The parallel port megacell implements the IEEE 1284 parallel port. The IEEE 1284 standard provides for high speed bi-directional communication between the PC and an external peripheral.

The parallel port defines 5 modes of data transfer. Each mode provides a method of transfering data in either the forward direction, reverse direction, or bi-directional data transfer. The defined modes are:

- Standard parallel port mode

- PS/2 parallel port mode

- Parallel port FIFO mode

- ECP parallel port mode

- Centronix Peripheral mode (Vendor specified mode)

Other modes defined in the IEEE 1284 standard like test mode and configuration mode are also supported.

## 7.6 Frame Memory Reduction Module

The CODEC Module consists of two Compressors and Decompressors, and a pass-through function (Zero Compressor).

Input to the compressors and decompressors comes from the system memory through the DMA Module. The output is saved in a 64-byte FIFO. The output from the FIFO can be returned to memory (to a different location than the input) or sent to the Video Interface/RET Module to be printed, but not both at the same time.

All compressors and decompressors operate on 32-byte (8-word) blocks of input data. If there are fewer bytes of data, the input must be padded to a multiple of 32 bytes. A Byte Counter is provided to limit the output if the padding would otherwise result in extra bytes after the desired output.

The CODEC's generate two signals to the processor to signal completion of the operation. One of these, "*proc\_done*", comes on when the CODEC is finished, but before the FIFO data has been transferred to memory or to the Video Interface. The other, "*done\_all*",' comes on after *proc\_done* when the FIFO becomes empty.

Much of the CODEC hardware is shared, so that only one compression or decompression can be in progress at a time.

#### 7.6.1 Zero Compressor

The Zero Compressor copies the input to the output unchanged. It can be used to print data that has not been compressed.

#### 7.6.2 Byte Compressor

This compressor is used for byte data, such as gray-scale images. It encodes the differences between bytes. It first computes the effectiveness of three types of differences for each 32-byte block. It then uses the method which results in maximum compression. If none of the three methods results in any compression, then the input data is copied to the output without compression. The encoding type is determined separately for each 32-byte block.

An SRAM, external to the W90100, must be provided to save one line of input data. The compressor uses this to form the difference between the current byte and bytes on the previous line.

The first scan line is treated differently, since there is no previous line with which to form differences. Instead, it uses an in-line difference and does not test to determine which encoding type would be best.

The maximum number of pixels (bytes) per line is determined by the size of the external SRAM. There are 16 address bits for the SRAM, so the maximum size is 65,535 bytes per line. The maximum number of output bytes is 16,777,215 bytes.

#### 7.6.3 JBIG Compressor

The JBIG compressor is used for processing one-bit images. It implements the ISO/IEC IS 11544 specification, also published as ITU-T T.82.

The CODEC does not process the 20-byte JBIG header. If required, the header must be processed by the CPU. For encoding, the header must be prefixed to the CODEC output; when decoding, the header must be stripped from the decoder input.

The same SRAM described in 7.6.2 is also used for this compressor. The maximum image width is 65,535 pixels (8192 Bytes) per line, assuming an SRAM of at least this size. The maximum number of lines is 65,535.

## 7.7 Image Enhancement Module

#### 7.7.1 Setup

Setup requirements consist of programming the control registers and downloading LUT (look\_up\_table) information into LUT memory. All internal register and memory locations can be read by the host CPU to check status and/or hardware integrity. In addition to the LUT memory and control registers, the Line Store memory can be written and read for testing. The memory map for the control registers and internal memories are:

| Memory Map                  | From (PA15:0) | To (PA15:0) |

|-----------------------------|---------------|-------------|

| Internal LUT (256 x 8)      | 0000          | 01FF        |

| Control Registers (5 x 16)  | 0400          | 040F        |

| Line Store Memory (4K x 16) | 4000          | 5FFF        |

#### POWER-UP CONDITIONS:

Control Registers are powered up in their inactive state. In order to make any mode operational, specific values must be written to the control registers as well as the LUT's, which will be powered up in a random state.

#### LOOK-UP TABLES:

Look-up tables are required to be loaded by the CPU. Final tables will be provided after characterization on a sampling of representative engines.

#### LINE MEMORY SIZE:

Line store memory is organized as 4K words. This is segmented by the hardware architecture according to what operating mode is selected.

| MODE        | BUFFERS      |

|-------------|--------------|

| 600x600x1   | 8            |

| 300x300x1   | 16           |

| 200x200x1   | 16           |

| 200x100x1   | 16           |

| 1200x1200x1 | 4            |

| 600x600x8   | NOT BUFFERED |

| 300x300x8   | 1            |

#### 7.7.2 Margin Offset Control:

Control register C contains the 11 bit register that sets the left-hand margin position of the image. The count will reflect the amount of 600dpi positions (1/600") from the selected edge of the beam detect (BD) signal, regardless of the mode selected.

#### 7.7.3 Vertical Margin Control

The top of page detection is controlled by fsync\_en (frame synch enable - control register A, bit 10) and frame sync, (fsynch). Fsync\_en is set by software to begin a page (lsynch' s will be ignored until the fsynch signal is received). When fsync\_en is high we wait for fsynch to go high and then lsynch clocks will begin counting the vertical margin counter. When the vertical margin counter equals the vertical margin top register, (control register E) data transfer will begin. The vertical margin bottom register, (control register F) data transfer will begin. The vertical margin bottom register, (control register F) data transfer will begin. The vertical margin bottom register, (control register F) data transfer will begin. The CPU is required to reset fsync\_en after it has moved the all of the line data into the W90100 chip and allowed it to image that data. (one, two, or three additional lines depending on mode). The CPU will then set fsync\_en again to prepare the fsynch logic for the next page synch signal, fsynch.

#### 7.7.4 Input Ports

The data input is parallel, eight bit. Data is transferred into the design on the rising edge of the parallel video clock. The first clock after the hysnc signal will transfer the first eight bits of data into the design.

7.7.5 Look-Up Table Memory (LUT):

To Load or Read the LUT memory the following bit in control registermust be set:

CPU2InternalLUT = Load LUT Memory (512x10)

Subsequent reading or writing to memory locations 0000-03FF will address the LUT memory, Data Bit 0 = LUT Bit 0. *What are LUT's for?* Look-up tables translate the fixed image values that are affected by engine linearity, temperature, aging, environmental, toner exhaustion, and other variables as well as features such as toner saver, paper type, type of input, etc. into values that will reproduce the highest quality image possible. The number of variables that influence the printed image are numerous and in order to correctly image the job these variables have to be compensated for. This is the job of the LUT memory.

#### 7.7.6 OPERATING MODES

#### 7.7.6.1 1200x1200x1

1200 Mode is selected by programming control register A bits [3:0] with a 1010. Source data must be in the two line format that can be used. The two line format requires that two lines of 1200 data must be transferred for each hysnc received by the design. The design will transfer two lines of sequential 1200 data per hysnc. The length of the lines is tracked via the line length register value (control register **D**, [11:0]) and when it reaches the programmed count it repeats the count for the second line. The CPU must program the line length (control register D) with the length of a single line of 1200 data into the Image Enhancement module.

To set up the W90100 for 1200 Enhanced the LUT memory must be loaded and the following control registers must be programmed:

| Control Register A                             | BITS          | VALUE   |

|------------------------------------------------|---------------|---------|

| Mode                                           | [3:0]         | 1010    |

| Mfunction (see table 2.0)                      | [6:5}         | XX      |

| vidkill                                        | 7             | 1       |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1  |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1  |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1  |

| Unused                                         | [12:11]       | 00      |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0 |

|                                                |               |         |

| Control Register <b>B</b>                      | BITS          | VALUE   |

| Other Control Registers              | BITS    | VALUE     |

|--------------------------------------|---------|-----------|

| C: Horizontal Margin Register        | [10:0]  | 0 - 3FFh  |

| C: Line Synch Width Register         | [15:11] | 0 - 1Fh   |

| D: Line Length Register              | [11:0]  | 0 - FFFh  |

| D: Unused                            | [15:12] | 0000      |

| E: Vertical Margin (Top) Register    | [15:0]  | 0 - FFFFh |

| F: Vertical Margin (Bottom) Register | [15:0]  | 0 - FFFFh |

[15:0]

00h

#### 7.7.6.2 600x600x1

Unused

600 Mode is selected by programming control register A,bits [3:0]. There are four different 600x1 operating modes to choose from. Oh is selected for enhanced text only, 1h is the test mode for 0h. 2h is for enhanced text and enhanced one bit gray scale. 3h is for unenhanced text and enhanced one bit gray scale. The CPU must program the line length (Control Register D) of a single line of 300 data into the Winbond chip.

To set up the Winbond chip for 600 Enhanced the LUT memory must be loaded and the following control registers must be programmed:

| Control Register A                             | BITS          | VALUE         |

|------------------------------------------------|---------------|---------------|

| Mode                                           | [3:0]         | 0h, 1h, 2, 3h |

| Mfunction (see table 2.0)                      | [6:5}         | 00            |

| vidkill                                        | 7             | 1             |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1        |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1        |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1        |

| Unused                                         | [12:11]       | 00            |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0       |

|                                                |               |               |

| Control Register <b>B</b>                      | BITS          | VALUE         |

| Unused                                         | [15:0]        | 00h           |

|                                                |               |               |

| Other Control Registers                        | BITS          | VALUE         |

| C: Horizontal Margin Register                  | [10:0]        | 0 - 3FFh      |

| C: Unused                                      | [15:11]       | 00000         |

| D: Line Length Register                        | [10:0]        | 0 - 3FFh      |

| D: Unused                                      | [15:12]       | 0000          |

| E: Vertical Margin (Top) Register              | [15:0]        | 0 - FFFFh     |

| F: Vertical Margin (Bottom) Register           | [15:0]        | 0 - FFFFh     |

#### 7.7.6.3 300x300x1

300 Mode is selected by programming control register A bits [3:0]. There are two different 300x1 operating modes to choose from. 4h is selected for enhanced text only, 5h is the test mode for 4h.

To set up the W90100 chip for 300 Enhanced the LUT memory must be loaded and the following control registers must be programmed:

| Control Register A                             | BITS          | VALUE     |

|------------------------------------------------|---------------|-----------|

| Mode                                           | [3:0]         | 4h, 5h    |

| Mfunction (see table 2.0)                      | [6:5}         | 00        |

| vidkill                                        | 7             | 1         |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1    |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1    |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1    |

| Unused                                         | [12:11]       | 00        |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0   |

| Control Register <b>B</b>                      | BITS          | VALUE     |

| Unused                                         | [15:0]        | 00h       |

|                                                | I             | 1         |

| Other Control Registers                        | BITS          | VALUE     |

| C: Horizontal Margin Register                  | [10:0]        | 0 - 3FFh  |

| C: Unused                                      | [15:11]       | 00000     |

| D: Line Length Register                        | [10:0]        | 0 - 3FFh  |

| D: Unused                                      | [15:12]       | 0000      |

| E: Vertical Margin (Top) Register              | [15:0]        | 0 - FFFFh |

**W90100F**

| F: Vertical Margin (Bottom) Register | [15:0] | 0 - FFFFh |

|--------------------------------------|--------|-----------|

|--------------------------------------|--------|-----------|

#### 7.7.6.4 200xNx1

200 Mode is selected by programming control register A bits [3:0]. There are four different 200x1 operating modes to choose from. 6h is selected for enhanced text only, 7h is the test mode for 6h. 8h is selected for 200x100x1 enhanced text. 9h is the test mode for 8h.

To set up the Winbond chip for 200 Enhanced the LUT memory must be loaded and the following control registers must be programmed:

| Control Register A                             | BITS          | VALUE          |

|------------------------------------------------|---------------|----------------|

| Mode                                           | [3:0]         | 6h, 7h, 8h, 9h |

| Mfunction (see table 2.0)                      | [6:5]         | 00             |

| vidkill                                        | 7             | 1              |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1         |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1         |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1         |

| Unused                                         | [12:11]       | 00             |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0        |

| Control Register <b>B</b> | BITS   | VALUE |

|---------------------------|--------|-------|

| Unused                    | [15:0] | 00h   |

| Other Control Registers              | BITS    | VALUE     |

|--------------------------------------|---------|-----------|

| C: Horizontal Margin Register        | [10:0]  | 0 - 3FFh  |

| C: Unused                            | [15:11] | 00000     |

| D: Line Length Register              | [10:0]  | 0 - 3FFh  |

| D: Unused                            | [15:12] | 0000      |

| E: Vertical Margin (Top) Register    | [15:0]  | 0 - FFFFh |

| F: Vertical Margin (Bottom) Register | [15:0]  | 0 - FFFFh |

#### 7.7.6.5 600x600x8

600x8 Mode is selected by programming control register bits [3:0].

To set up the W90100 chip for 600x8 the LUT memory must be loaded and the following control registers must be programmed:

| Control Register A                             | BITS          | VALUE    |

|------------------------------------------------|---------------|----------|

| Mode                                           | [3:0]         | Bh       |

| Mfunction (see table 2.0)                      | [6:5}         | 00       |

| vidkill                                        | 7             | 1        |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1   |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1   |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1   |

| Unused                                         | [12:11]       | 00       |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0  |

| Control Register <b>B</b>                      | BITS          | VALUE    |

| Unused                                         | [15:0]        | 00h      |

|                                                | TT            |          |

| Other Control Registers                        | BITS          | VALUE    |

| C: Horizontal Margin Register                  | [10:0]        | 0 - 3FFh |

| C: Unused                            | [15:11] | 00000     |

|--------------------------------------|---------|-----------|

| D: Line Length Register              | [10:0]  | 0 - 3FFh  |

| D: Unused                            | [15:12] | 0000      |

| E: Vertical Margin (Top) Register    | [15:0]  | 0 - FFFFh |

| F: Vertical Margin (Bottom) Register | [15:0]  | 0 - FFFFh |

#### 7.7.6.5 300x300x8

300x8 Mode is selected by programming control register 'A' bits [3:0]. The CPU must program the line length (Control Register '**D**') of a single line of 300 data into the Winbond chip.

To set up the Winbond chip for 300x8 Enhanced the LUT memory must be loaded and the following control registers must be programmed:

| Control Register 'A'                           | BITS          | VALUE   |

|------------------------------------------------|---------------|---------|

| Mode                                           | [3:0]         | Ch      |

| Mfunction (see table 2.0)                      | [6:5}         | 00      |

| vidkill                                        | 7             | 1       |

| bdedge ( $0 = rising edge, 1 = falling edge$ ) | 8             | 0 or 1  |

| vidpol ( $0 = normal, 1 = inverse$ )           | 9             | 0 or 1  |

| fsync_en (see paragraph for operational desc)  | 10            | 0 or 1  |

| Unused                                         | [12:11]       | 00      |

| Other                                          | 4, 13, 14, 15 | 0,0,0,0 |

| Control Register 'B' | BITS   | VALUE |

|----------------------|--------|-------|

| Unused               | [15:0] | 00h   |

| Other Control Registers              | BITS    | VALUE     |

|--------------------------------------|---------|-----------|

| C: Horizontal Margin Register        | [10:0]  | 0 - 3FFh  |

| C: Unused                            | [15:11] | 00000     |

| D: Line Length Register              | [10:0]  | 0 - 3FFh  |

| D: Unused                            | [15:12] | 0000      |

| E: Vertical Margin (Top) Register    | [15:0]  | 0 - FFFFh |

| F: Vertical Margin (Bottom) Register | [15:0]  | 0 - FFFFh |

#### 7.7.6.6 ONE BIT (600/300/200) TEST MODES

Test modes are different from normal one bit modes in that they bypass the Edge Enhancement Unit, (EEU). The input data is sampled just prior to the LUT memories. Selecting 600x600x1t, 600x600x1tg, 300x300x1t, 200x200x1t, or 200x100x1t one bit modes in register A will operate this way. The purpose of the test mode is to be able to bypass the EEU logic and present the assembled data directly to the modulator in order to isolate faults. Output will appear exactly like the input bit map.

### 8. Control and Status Register

## 8.1 CPU Registers

The W90100 CPU core implements all the registers needed for a Level 0 processor as defined in the PA-RISC specifications. Some registers or register bits are not needed in a Level 0 processor and are defined as nonexistent registers or register bits. The W90100 CPU implements three AIRs (Architecture Invisible Registers) that can be accessed by executing DIAG instructions.

#### 8.1.1 General registers

Thirty-two 32-bit general registers provide the central resource for all computation. They are numbered GR 0 through GR 31, and are available to all program at all privilege levels. GR 0, when referenced as source operand, delivers zeros. When GR 0 is used as destination, the result is discarded. GR 1 is the target of the ADD IMMEDIATE LEFT instruction. GR 31 is the instruction address offset link register for the base relative interspace procedure call instruction. GR 1 and GR 31 can also be used as general register.

|       | 0 3                                  | 1 |

|-------|--------------------------------------|---|

| GR 0  | Permanent zero                       |   |

| GR 1  | Target for ADDIL or General use      |   |

| GR 2  | General use                          |   |

|       | •                                    |   |

|       | •                                    |   |

|       | •                                    |   |

| GR 30 | General use                          |   |

| GR 31 | Link register for BLE or General use |   |

#### FIGURE 8.1 GENERAL REGISTERS

#### 8.1.2 Shadow registers

W90100 CPU core provides seven registers called shadow registers as defined in the PA-RISC architecture. The contents of GR1,8,9,16,17,24 and 25 are copied upon interruptions. Shadow registers reduce the state save and restore time by eliminating the need for general register saves and restores in interruption handlers. The behavior of the shadow registers is described below.

Before entering interrupt routine: Contents of seven general registers are copied into shadow registers in one cycle.

When executing RFIR: Contents of shadow registers are copied into general registers automatically in one cycle.

#### 8.1.3 Processor Status Word (PSW)

The processor state of W90K is encoded in a 32-bit register called the Processor Status Word (PSW). The format of PSW is shown in figure 8.2. The old value of the PSW is saved in the Interrupt Processor Status Word (IPSW) when interruption occurs. The PSW is set to the contents of the IPSW by the RFIR (RETURN FROM INTERRUPTION and RESTORE) instruction.

| 0     | 1 | 2 | 4                                                                                                                                                                  | 5                                     | 6      | 7     | 8     | 9     | 1<br>0 | 1<br>1 | 1<br>2 | 1<br>3 | 1<br>4 | 1<br>5 | 1<br>6              |                    | 2<br>3  | 2<br>4 | 2<br>5   | 2<br>6 | 2<br>7 | 2<br>8 | 2<br>9 | 3<br>0 | 3<br>1 |

|-------|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|-------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|--------------------|---------|--------|----------|--------|--------|--------|--------|--------|--------|

| Ŷ     | Z |   | rv                                                                                                                                                                 | E                                     | s      | Ť     | н     | L     | N      | X      | B      | C      | V      | M      |                     | <br>С/В            | 0       | rv     | G        | F      | R      | Q      | P      | D      | Γ.     |

| Field | ł |   |                                                                                                                                                                    |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| rv    |   |   | Rese                                                                                                                                                               | rved                                  | bits   |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| Υ     |   |   | Data                                                                                                                                                               | deb                                   | ug tra | ap d  | isabl | e.    |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| Ζ     |   |   | Instru                                                                                                                                                             | uctio                                 | n del  | bug   | trap  | disat | ole.   |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| Е     |   |   |                                                                                                                                                                    |                                       |        |       |       |       |        |        |        |        |        |        | es an               | d loads            | /store  | es are | e little | e en   | dian.  | The    | E bi   | t afte | ۶r     |

| S     |   |   | RESI                                                                                                                                                               |                                       |        |       |       |       |        |        |        |        |        |        | dabla               | only h             | ( 00 d  |        |          |        | the    | moot   |        | logo   | 4      |

| 3     |   |   |                                                                                                                                                                    |                                       |        |       |       |       |        |        |        |        |        |        |                     | only by<br>ting at |         |        |          |        |        | mosi   | privi  | liege  | a      |

| т     |   |   |                                                                                                                                                                    |                                       |        |       |       |       |        |        |        |        |        |        |                     | ted wit            |         |        |          |        |        |        |        |        |        |

| н     |   |   | Highe                                                                                                                                                              |                                       |        |       |       |       |        |        |        |        |        | 10 10  | mina                |                    | ii u ii | interr | bran     |        | սբ.    |        |        |        | -      |

| L     |   |   | Lowe                                                                                                                                                               |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        | -      |

| N     |   |   | Nullif                                                                                                                                                             |                                       |        |       |       |       |        |        |        | d whe  | en th  | is bi  | is 1.               |                    |         |        |          |        |        |        |        |        |        |

| Х     |   |   | Non-                                                                                                                                                               | · · · · · · · · · · · · · · · · · · · |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| В     |   |   |                                                                                                                                                                    |                                       |        | -     |       |       | set t  | 011    | oy ar  | ny ta  | ken l  | oran   | ch inst             | tructior           | and     | set t  | o 0 c    | other  | wise   | ).     |        |        |        |

| С     |   |   | Non-                                                                                                                                                               |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| V     |   |   | Divide<br>non-r                                                                                                                                                    |                                       |        |       |       |       |        | jer p  | orimit | ive ir | nstru  | ction  | recor               | ds inte            | rmed    | ate s  | status   | s in t | this I | oit to | prov   | /ide   | а      |

| Μ     |   |   |                                                                                                                                                                    |                                       |        |       |       |       |        |        |        |        |        |        |                     | hine C             |         |        | PMCs     | s) are | e ma   | sked   | . Nor  | rmall  | у      |

| C/E   | 6 |   |                                                                                                                                                                    | //bori                                | row    | bits. | The   | se b  | its a  | ire i  | ıpda   |        |        |        |                     | ictions            |         |        | corre    | espc   | ondin  | g ca   | rry/b  | orro   | v      |

| G     |   |   | Debu                                                                                                                                                               | ig tra                                | ap er  | nable | ).    |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| F     |   |   | Non-                                                                                                                                                               |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| R     |   |   | Recovery counter enable. When 1, recovery counter traps occur if bit 0 of the recovery counter is a 1. This bit also enables decrementing of the recovery counter. |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| Q     |   |   | Interr                                                                                                                                                             | upts                                  | state  | coll  | ectio | n en  | able   | . Wr   | en 1   | , inte | errup  | tion   | state               | is colle           | cted.   |        |          |        |        |        |        |        |        |

| Ρ     |   |   | Non-                                                                                                                                                               |                                       |        | -     |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| D     |   |   | Non-                                                                                                                                                               |                                       |        |       |       |       |        |        |        |        |        |        |                     |                    |         |        |          |        |        |        |        |        |        |

| Ι     |   |   |                                                                                                                                                                    |                                       |        | •     |       |       |        |        |        | •      |        |        | iority i<br>nterrup | machin<br>otion.   | e che   | eck in | terru    | uptio  | n un   | mask   | . Wh   | nen 1  | ,      |

## FIGURE 8.2 PROCESSOR STATUS WORD

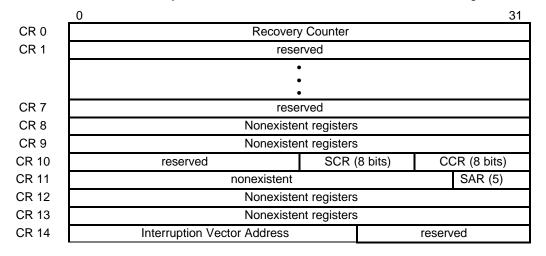

8.1.4 Control registers

There are twenty-five control registers in W90100, numbered CR0, and CR8 through CR31, which contain system state information. Figure 8.3 shows the control registers. The access of CR 11, 16, 26, and 27 are described in the following table (table 8.4). Those control registers not listed in table 8.4 are only accessible by code executing at the most privileged level. Control registers 1 through 7 are reserved registers. The unused bits of the Coprocessor Configuration Register are reserved bits. The unused bits of the Shift Amount Register are nonexistent bits. In Level systems, CRs 8, 9, 12, 13, 17, and 20 are nonexistent registers.

| CR 15     | External Interrupt Enable Masks                    |                                               |  |  |  |  |  |

|-----------|----------------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| CR 16     | Interval Timer                                     |                                               |  |  |  |  |  |

| CR 17     | Nonexistent registers                              |                                               |  |  |  |  |  |

| CR 18     |                                                    | Interruption Instruction Address Offset Queue |  |  |  |  |  |

| CR 19     |                                                    | Interruption Instruction Register             |  |  |  |  |  |

| CR 20     |                                                    | Nonexistent registers                         |  |  |  |  |  |

| CR 21     |                                                    | Interruption Offset Register                  |  |  |  |  |  |

| CR 22     |                                                    | Interruption Processor Status Word            |  |  |  |  |  |

| CR 23     |                                                    | External Interrupt Request Register           |  |  |  |  |  |

| CR 24     | Temporary Registers                                |                                               |  |  |  |  |  |

|           | •                                                  |                                               |  |  |  |  |  |

|           |                                                    | •                                             |  |  |  |  |  |

| CR 31     |                                                    | Temporary Registers                           |  |  |  |  |  |

| FIGURE 8. | 3 CONTROL REG                                      | ISTERS                                        |  |  |  |  |  |

|           |                                                    | Privilege level for the access                |  |  |  |  |  |

|           | CR 11 read/write at any privilege level            |                                               |  |  |  |  |  |

|           | CR 16 PSW 'S'=0: read/write by any privilege level |                                               |  |  |  |  |  |

|           | PSW 'S'=1: read/write by privileged software       |                                               |  |  |  |  |  |

|           | CR 26, 27 readable at any privilege level          |                                               |  |  |  |  |  |

|           |                                                    | writable at the most privileged level         |  |  |  |  |  |

|           | Others                                             | Accessible only at most privileged level      |  |  |  |  |  |

TABLE 8.4 ACCESS OF CONTROL REGISTERS

| 8     | 8.1.5 W90100 External Interrupt Request register (EIRR; CR23) |           |                                                         |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------|-----------|---------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit # |                                                               |           | Description                                             |  |  |  |  |  |  |  |  |

|       |                                                               | Interrupt |                                                         |  |  |  |  |  |  |  |  |

| 0     | 00000                                                         | Timer INT | Interval Timer (CR16) Interrupt Request: the same as    |  |  |  |  |  |  |  |  |

|       |                                                               |           | W90K                                                    |  |  |  |  |  |  |  |  |